#

#### Lecture 7: Part 1: Fabrication of Silicon Solar Cells Part 2: Thin Film Crystalline Silicon Solar Cells

#### Prof. Dr. Bryce S. Richards

Institute of Microstructure Technology (IMT), Hermann-von-Helmholtz-Platz 1, 76344 Eggenstein-Leopoldshafen Light Technology Institute (LTI), Engesserstrasse 13, Building 30.34, 76131 Karlsruhe

KIT Focus Optics & Photonics

KIT – Universität des Landes Baden-Württemberg und nationales Forschungszentrum in der Helmholtz-Gemeinschaft

### Silicon – Long History

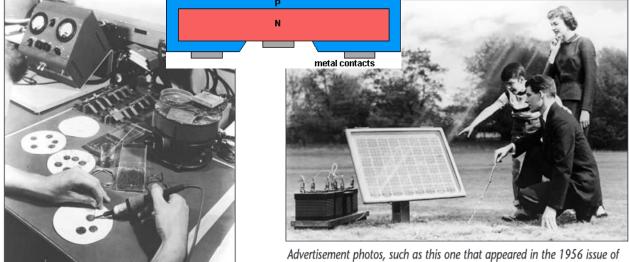

Forefather of today's Si solar cell date to 1954 by researchers at Bell Laboratories (USA). Cells had a <u>diffused junction</u> and both *n*- and *p*-type contacts on the rear  $\Rightarrow \eta = 6\%$  (15x that of earlier devices). First application for space  $\Rightarrow$  remained major market until early 1970's

Advertisement photos, such as this one that appeared in the 1956 issue of Look Magazine, show off the "Bell Solar Battery" to the American public.

Source:

http://www.pveducation.org/pvcdrom/manufacturing/early-silicon-solar-cells

2

http://www.nrel.gov/education/pdfs/educational\_resources/high\_school/solar\_cell\_history.pdf

#### Silicon – Long History

The Bell Solar Battery.

silicon wafers turns sunshine into 50 watts of electricity. The battery's 6% efficiency approaches that of gasoline and steam engines and will be increased. Theoretically the battery will never wear out. It is still in the early experimental stage.

Bell Solar Battery

Source: http://www.radiomuseum.org/forumdata/users/6435/Cxt/07\_cell.jpg

115

### **Refining Silicon**

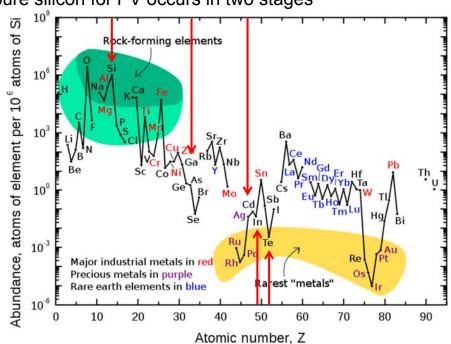

Silicon dioxide  $(SiO_2) \Rightarrow$  most abundant mineral in earth's crust  $\Rightarrow$  manufacture of hyperpure silicon for PV occurs in two stages

- 1. Oxygen is removed to produce <u>metallurgical grade</u> <u>silicon</u>

- 2. Further refined to produce <u>electronic</u> <u>grade silicon</u>

An intermediate grade with impurity levels between 1) and 2) above is often termed solar grade silicon

4

Source: http://en.wikipedia.org/wiki/Abundance\_of\_the\_chemical\_elements

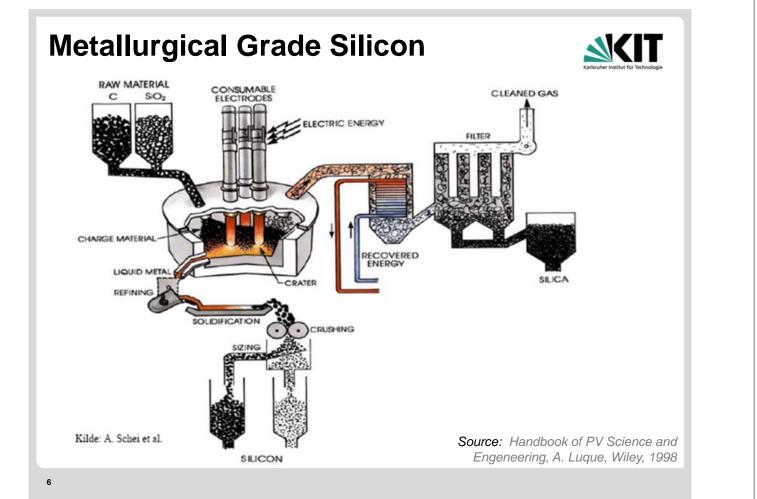

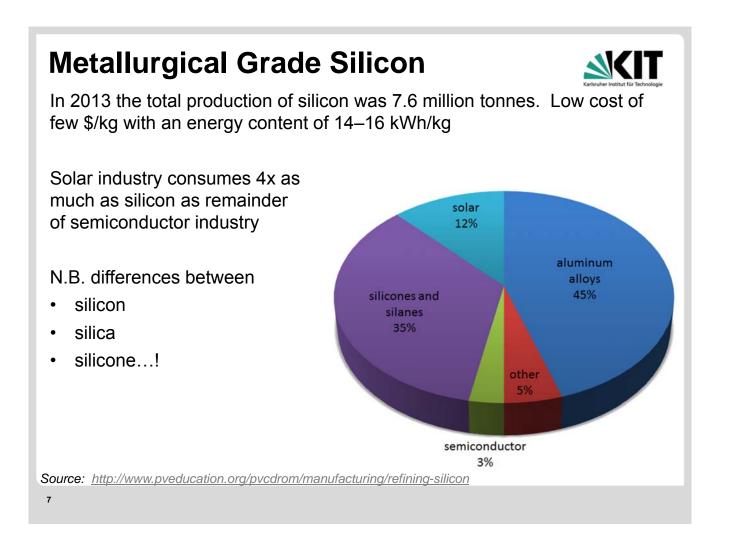

### **Metallurgical Grade Silicon**

Silica  $(SiO_2)$  occurs naturally as quartz. Most common raw material for electronic grade is high purity quartz rock, but could also use beach sand. Ideally, silica has low concentrations of Fe, AI and other metals.

Silica reduced (oxygen removed) through reaction with carbon (coal, charcoal) and heating to 1500-2000 °C in an electrode arc furnace

$\text{SiO}_2 + \text{C} \rightarrow \text{Si} + \text{CO}_2$

5

Result is metallugical grade silicon (MG-Si)  $\Rightarrow$  98% pure and used extensively in the metallurgical industry

#### **Metallurgical Grade Silicon**

8

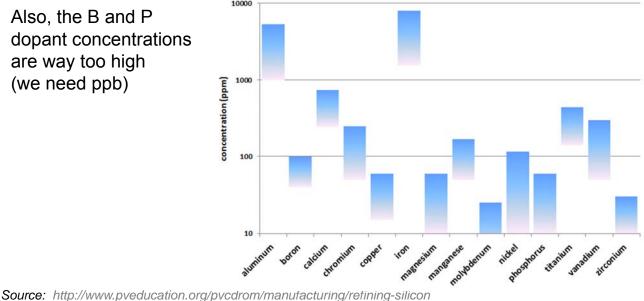

2% impurities are mainly carbon, alkali-earth and transition metals and hundreds of ppm of B and P

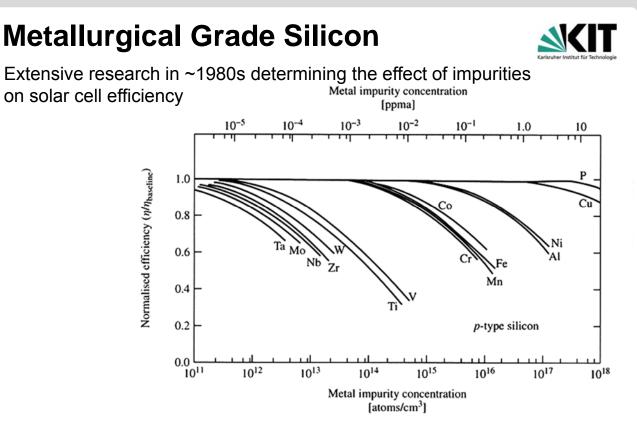

Transition metals in silicon result in deep levels in bandgap  $\Rightarrow$  high recombination activity makes MG-Si unsuitable for use in electronics

**Figure 5.11** Solar cell efficiency versus impurity concentration for 4 ohm cm p-base devices [30]. Reproduced from Davis Jr. J *et al.*, *IEEE Trans. Electron Devices* © 1980 IEEE

#### **Electronic Grade Silicon**

Small amount of MG-Si further refined for semiconductor industry. Powdered MG-Si reacted with anhydrous HCI at 300 °C in a fluidized bed reactor to form trichlorosilane (SiHCl<sub>3</sub>)

Si + 3HCl  $\rightarrow$  SiHCl<sub>3</sub> + H<sub>2</sub>

Impurities such as Fe, AI, and B react to form halides (e.g.  $FeCI_3$ ,  $AICI_3$ ,...). SiHCI<sub>3</sub> has low boiling point of 31.8 °C  $\Rightarrow$  distillation used to purify SiHCI<sub>3</sub> from impurity halides  $\Rightarrow$  now has < 1 ppb of electrically active impurities.

Finally, pure SiHCl<sub>3</sub> reacts with hydrogen at  $1100^{\circ}$ C for  $\sim 200 - 300$  hours to produce a very pure silicon

$SiHCl_3 + H_2 \rightarrow Si + 3 HCl$

9

#### **Electronic Grade Silicon (EG-Si)** Cooling medium Reaction inside large vacuum chambers and Si deposited onto thin polysilicon rods to External produce high-purity polysilicon (Poly) envelope silicon (~Ø200mm). "Siemens process" first rods developed 1960's Rods of EG-Si then broken $\Rightarrow$ form feedstock for crystallisation process Internal wall Cooling medium Production requires a lot of energy. Electrical contact to resistive Solar cells can tolerate higher levels Reactor Reactor inlet outlet heating SiHCl<sub>3</sub> SiCl<sub>4</sub> of impurities than for IC fabrication (H<sub>2</sub>) (SiHCl<sub>3</sub>) $H_2$ $\Rightarrow$ proposals for creating "solar-grade" silicon (SiH<sub>2</sub>Cl<sub>3</sub>) HCl

Source: Handbook of PV Science and Engeneering, A. Luque, Wiley, 1998

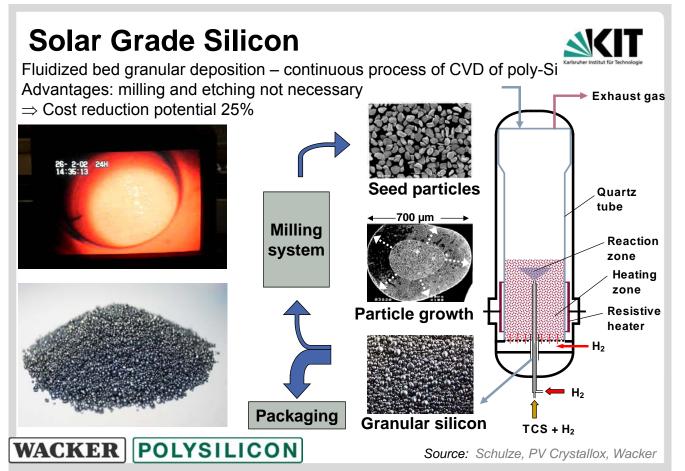

### Solar Grade Silicon

In this continuous process, silicon is deposited from SiHCl<sub>3</sub> on Si seed crystals ( $\emptyset$ 0.3 – 0.7 mm)  $\Rightarrow$  specific surface area greater than silicon rod in Siemens process

Granules of poly-silicon then continuously "harvested" from the reactor

The fluidized bed process is economic for "solar" poly-silicon for several reasons:

- deposits more silicon in the same time than Siemens process

- reduced electrical heating power

- reactor doesn't need to be cooled to open to remove silicon

- · eliminates the costly accidental breakage of rods

- granules also better suited for further processing

$\Rightarrow$  so far SG-Si only used in the development and pilot production

13

### Single Crystal Silicon

Czochralski (Cz) process  $\Rightarrow$  most commonly used by both solar IC industry to produce single crystal ingot (process shown below). The use of quartz crucibles in manufacture of Cz Si results in

$\Rightarrow$  incorporation of ppm (10<sup>18</sup> cm<sup>-3</sup>) of O into Si ingot

$\Rightarrow$  creates complex with B dopant that degrades *L* over time (does

not happen in n-type ingots fabricated with phosphorus)

Rejected "tops" and "tails" from IC industry recycled into solar industry

Energy content of Cz c-Si ~210 kWh per kg of EG-Si

Source: <u>http://www.pveducation.org/pvcdrom/</u> manufacturing/czochralski-silicon

#### Single Crystal Silicon

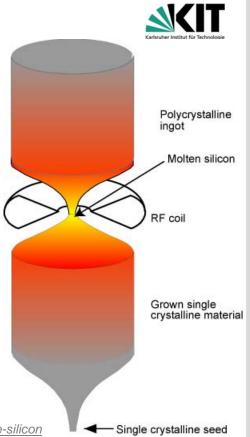

To avoid B-O complex or for other ultra-pure silicon  $\Rightarrow$  use float zone (FZ) process instead

Process: molten region is slowly passed along rod of silicon  $\Rightarrow$  impurities tend to stay in molten region rather than be incorporated into solidified region  $\Rightarrow$  allows a very pure single crystal region to remain after the molten region has passed

Due to the difficulty in growing large diameter ingots and the often higher cost, FZ wafers typically only used for laboratory cells and are less common in commercial production

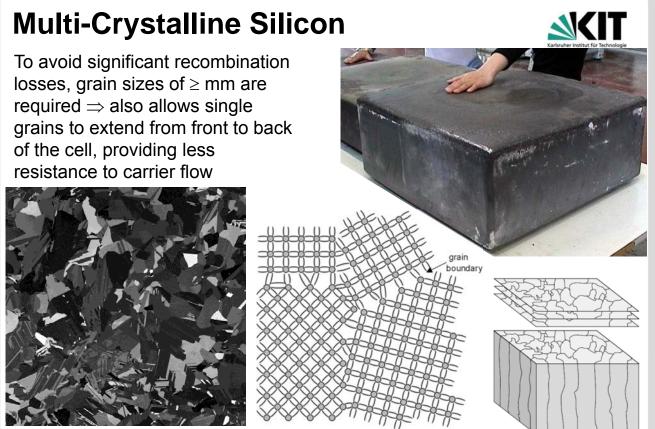

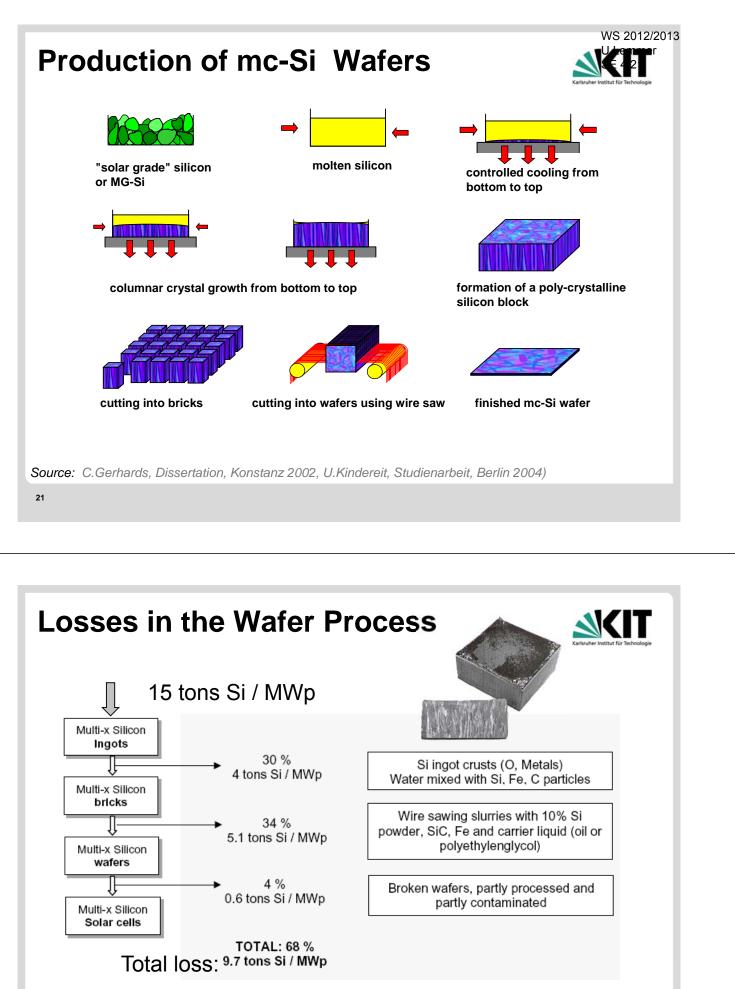

### **Multi-Crystalline Silicon**

Can also produce multicrystalline silicon (mc-Si) which is

- ✓ simpler,

- ☑ less energy intensive (8-15 kWh/kg), and

- 🗹 cheaper, but...

- Image: Image:

Grain boundaries introduce

- high localised regions of recombination due to introduction of extra defect energy levels into bandgap ⇒ reduces L

- Barriers to flow of carriers and providing shunting paths for current flow across *p-n* junction

Source: http://www.pveducation.org/pvcdrom/manufacturing/float-zone-silicon

17

Source: http://www.pveducation.org/pvcdrom/manufacturing/multi-crystalline-silicon

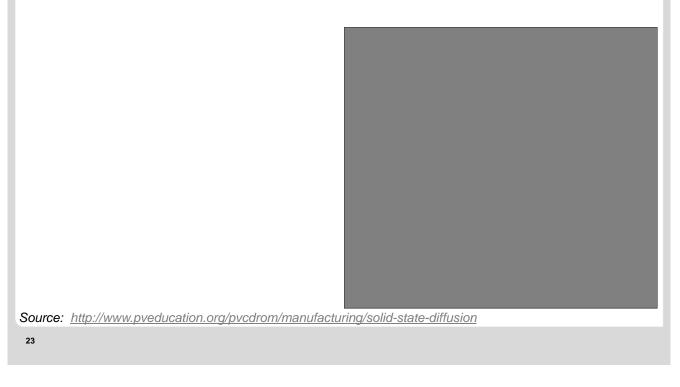

Once ingot is grown  $\Rightarrow$  then sliced up into wafers. For mc-Si, large slabs are then sliced up first into smaller "bricks" using diamond saw. Wafers then realised using a wire saw with SiC slurry

Source: <u>http://www.pveducation.org/node/496</u> 19

### Wafer Slicing

cutting wires

silicon brick attached with

wire guides

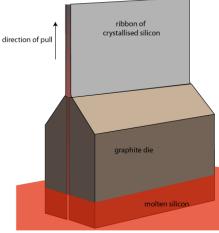

The "kerf" losses due the sawing can be high  $\Rightarrow$  other processes investigated to grow wafers from the outset  $\Rightarrow$  avoid cutting process

Edge Defined Film Fed Growth (EFG) technique uses a die to define thickness of a silicon sheet. Careful adjustment of the temperature profile of graphite die causes the Si sheets to crystallize with large grains.

Source: http://www.pveducation.org/pvcdrom/manufacturing/other-wafering-techniques

Total of 5.3 tons (32%) goes into solar cells

Source: D. Sarti and R. Einhaus, Photowatt (2002)

### **Solid State Diffusion**

Process for introducing dopant atoms into semiconductors. In Si solar cell processing, typically start with a uniformly doped *p*-type wafer (the "base"). The *n*-type emitter layer is formed through phosphorus doping

### **Solid State Diffusion**

The diffusion process follows Fick's law:

$$j = -D\frac{\partial N}{\partial x}$$

where

*j* = flux density (atoms cm<sup>-2</sup>), *D* = diffusion coefficient (cm<sup>2</sup> s<sup>-1</sup>) N = concentration volume (atoms cm<sup>-3</sup>) *x* = distance (cm)

Typically, what happens is that the Si wafer is placed in a furnace with unlimited source (e.g. phosphorus saturated carrier gas), and then turning off the source and driving in the phosphorus atoms further into the wafer

# **Solid State Diffusion**

<u>Diffusion from an Unlimited Source</u>: to produce a shallow junction with a very high surface concentration of P atoms, described by complementary error function

$$N(x,t) = N_0 erfc \frac{x}{2\sqrt{Dt}}$$

where

$N_0$  = impurity concentration at surface (atoms cm<sup>-3</sup>)

$$t = time (sec)$$

Simple one-step diffusion is useful where there is no surface passivation of the device.

Source: http://en.wikipedia.org/wiki/Error function

25

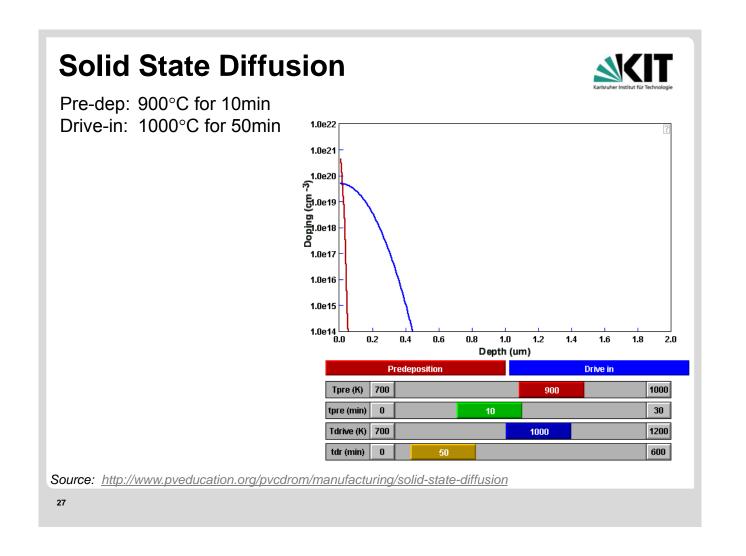

# Solid State Diffusion

Diffusion from a Limited Source: consists of two-step process

- 1. a short pre-deposition as outlined above, followed by

- 2. a longer drive-in at a higher temperature to provide a deep and lightlydoped emitter

If the drive-in is at a higher temperature the final profile is a Gaussian, described by:  $O_0 = \left(\frac{x}{100}\right)^2$

$$N(x,t) = \frac{Q_0}{\sqrt{\pi Dt}} e^{-\left(\frac{x}{2}\sqrt{Dt}\right)^2}$$

where

$Q_0$  = is atoms introduced in the pre-deposition (atoms cm<sup>-2</sup>)

#### **Solid State Diffusion** Pre-dep: 900°C for 10min Drive-in: 1000°C for 170min 1.0e22 1.0e21 1.0e20 ເຈົ **문**1.0e19 ) 6ujd.0e18 00 1.0e17 1.0e16 1.0e15 1.0e14 ----0.0 0.2 0.6 0.8 1.0 2.0 0.4 1.2 1.4 1.6 1.8 Depth (um) Predeposition Drive in Трге (К) 700 1000 900 30 0 tpre (min) 10 Tdrive (K) 700 1000 1200 tdr (min) 600 0

Source: http://www.pveducation.org/pvcdrom/manufacturing/solid-state-diffusion

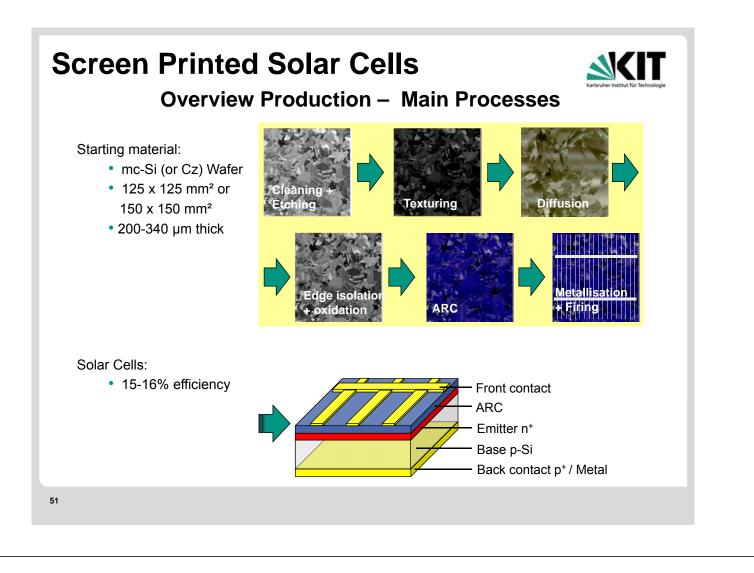

Screen-printed solar cells first developed in 1970's  $\Rightarrow$  most mature solar cell fabrication technology  $\Rightarrow$  currently dominate the market for terrestrial PV. Key advantage of screen-printing is the simplicity of process. Basic process in animation below (since improved upon by many manufacturers and research laboratories)

Summary animation:

Source: http://www.pveducation.org/pvcdrom/manufacturing/screen-printed

29

# **Screen Printed Solar Cells**

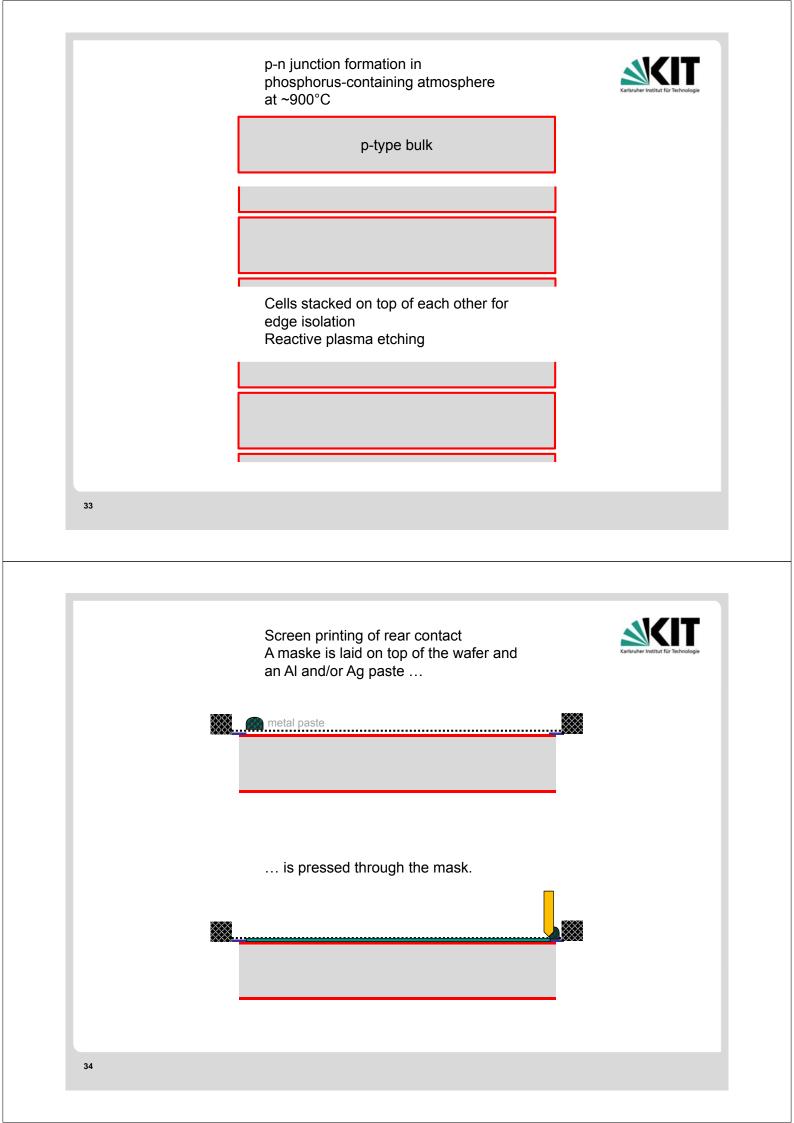

Fabrication sequence:

- 1. Sawing of monocrystalline or mc-Si ingots to produce wafers

- Etching to remove saw damage (20µm from either side of wafer etched off)

- Texturing (only for mono-Si)

<100> oriented Si wafers are textured, results in exposing the <111> crystal planes as pyramids 1-10µm high using KOH-based etch

- 4. Emitter diffusion

typically performed as phosphorus diffusion to achieve *n*-type emitter in a p-type (boron-doped) substrate. Conducted in a tube furnace at about 900°C. Followed by i) plasma etching of the undesired junction around the edge and ii) etching off the phosphorus glass ( $P_2O_5$ )

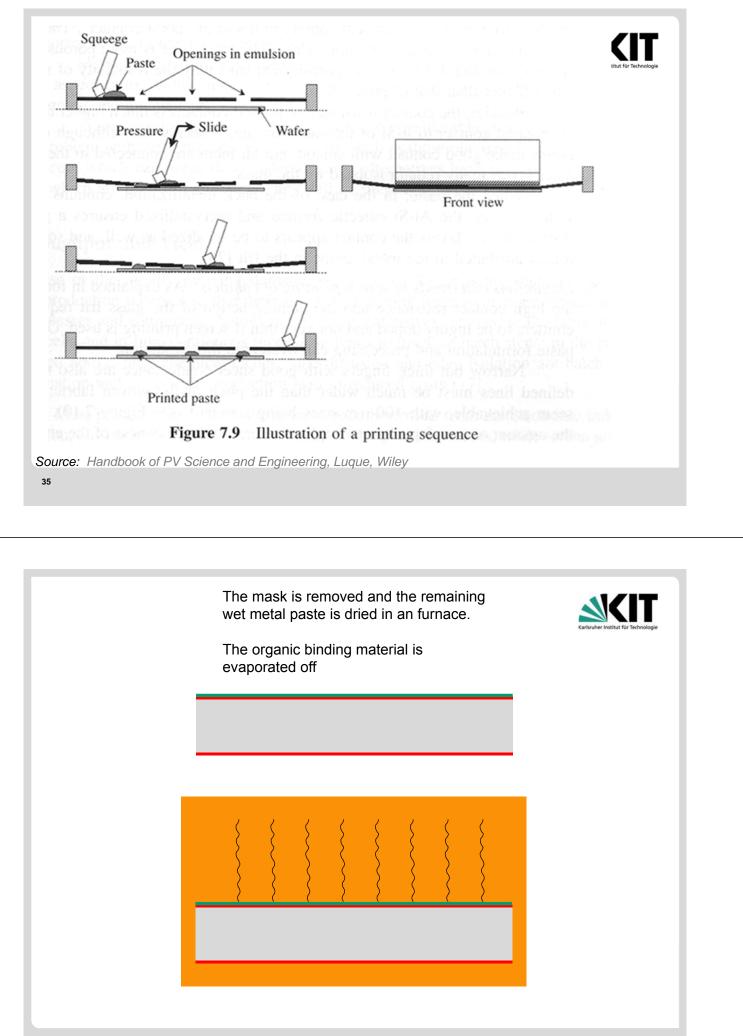

| Screen Printed Solar Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>Passivation and ARC<br/>the most common material used as an ARC (a-SiN<sub>x</sub>:H) can also afford<br/>some passivation of surface and bulk defects (via</li> </ol>                                                                                                                                                                                                                                                                                               |

| <ol> <li>Printing<br/>of pastes – contain metal particles (5-10 μm Ag oder Al) as well as<br/>glass frit to help etch through the SiN<sub>x</sub> layer</li> </ol>                                                                                                                                                                                                                                                                                                            |

| <ul> <li>7. Firing <ul> <li>of pastes at high T, with the glass frit also improving adhesion.</li> <li>Advantages of screen printing: higher metal yield</li> <li>Disadvantages: <ul> <li>Grids can't be smaller than 100µm</li> <li>Particle nature of metal limits conductivity</li> </ul> </li> <li>⇒ but still the standard process in industry</li> <li>⇒ steps 6. und 7. are repeated twice – once for back contact and once for the front contact</li> </ul></li></ul> |

| 8. Measurement under "solar simulator" and sorting                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Additional step: Al or B doped BSF sometimes performed                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <i>p</i> -type (1 × 16 B atoms/cm <sup>3</sup> ) wafer<br>with ~300 $\mu$ m thickness.                                                                                                                                                                                                                                                                                                                                                                                        |

| 10 cm                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Etching away the saw damage

At higher temperatures, contact between the metal and silicon is made (diffusion) Which converts the rear n-type layer to p-type The cell is now turned over to the front side 37 Front contact is produced in a similar way to the rear, but with a different mask that specifies the desired grid contact 383 \*\* Hopefully low shading is achieved and this grid pattern is now fired

Many variations to animation shown above, which give higher efficiencies, lower costs or both. Some of these specific techniques described below

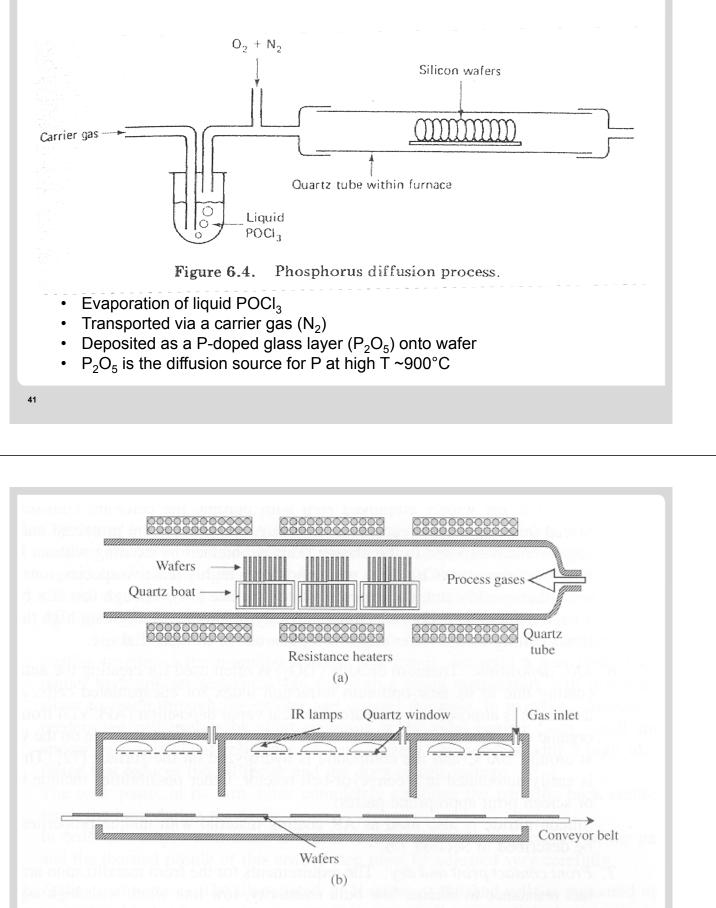

#### Phosphorus Diffusion:

Screen-printed solar cells typically use a simple homogeneous diffusion (x-y direction) to form the emitter  $\Rightarrow$  doping is same beneath metal contacts and between fingers.

To maintain low contact resistance ( $R_S$ ), a high surface concentration of P is required below the screen-printed contact. But, the high surface concentration of P produces a "dead layer" that reduces the EQE of the cell in the UV/blue region.

Developments: reduced  $R_{\rm S}$  and improved blue response achieved via newer cell designs that

- i) can contact shallower emitters

- ii) possess "selective emitters" ⇒ with higher doping below the metal contacts have also been proposed (makes process more complicated as it involves a subsequent alignment step)

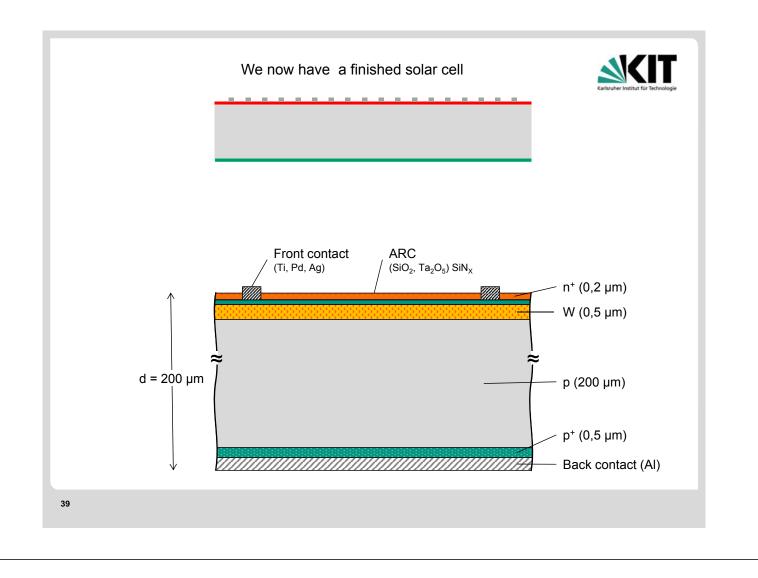

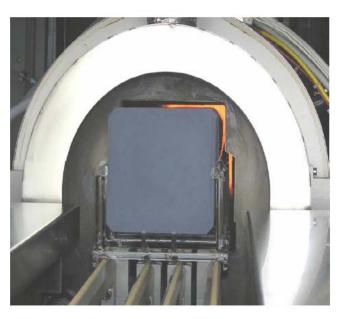

# Phosphorus Diffusion: *p-n* junction formation

**Figure 7.7** (a) A quartz furnace; and (b) a belt furnace for the diffusion of phosphorus *Source:* Handbook of PV Science and Engineering, Luque, Wiley

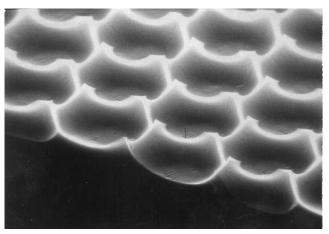

Surface Texturing to Reduce Reflection:

While monocrystalline Si wafers are easily textured with a NaOH or KOH based chemical etch to from pyramids and reduce reflection, same process is only marginally effective on the randomly orientated grains of mc-Si.

Various schemes have been proposed to texture mc-Si material:

- mechanical texturing of the wafer surface with cutting tools or lasers

- isotropic chemical etching based on defects rather than crystal orientation

- isotropic chemical etching in combination with a photolithographic mask \_\_\_\_\_

- plasma etching

Source: http://www.pveducation.org/pvcdrom/design/surface-texturing

43

Antireflection Coatings and Fire Through Contacts:

ARCs are particularly beneficial for mc-Si since it cannot be easily textured. Two common antireflection coatings are titanium dioxide  $(TiO_2)$  and silicon nitride  $(SiN_x)$ . The coatings are applied through techniques like spraying or chemical vapour deposition (CVD). In addition to the optical benefits, dielectric coatings can also improve the electrical properties of the cell by surface passivation.

By screen-printing over the ARC with a paste containing cutting agents, the metal contacts can fire though the ARC and bond to the underlying silicon. This simplifies processing and has the added advantage of contacting shallower emitters

#### Edge Isolation

Various techniques have been investigated for edge isolation such as plasma etching, laser cutting, or masking the border to prevent diffusion from occurring around the edge in the first place

45

#### **Screen Printed Solar Cells**

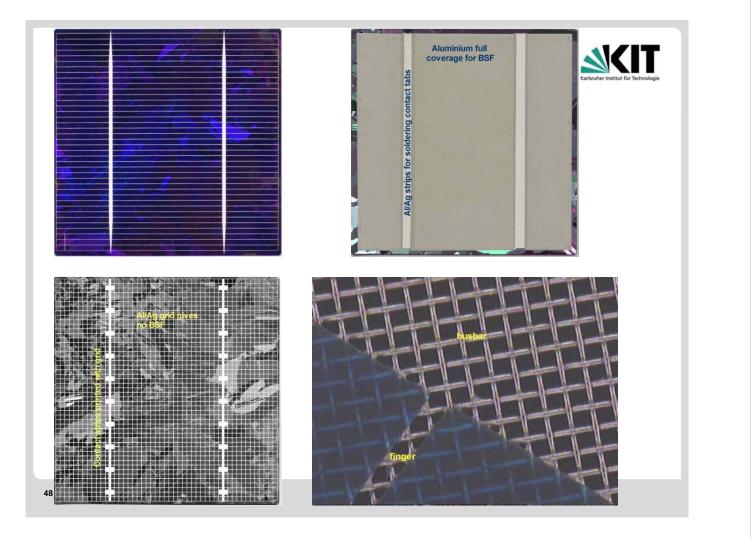

#### Rear Contact

A full AI layer printed on the rear on the cell, with subsequent alloying through firing, produces a BSF and improves the cell bulk through "gettering" (a way of disabling the effect of impurities). However, the AI is expensive and a second print of AI/Ag is required for solderable contact. In most production, the rear contact is simply made using a AI/Ag grid printed in a single step.

#### **Substrate**

Screen-printing has been used on a variety of substrates. The simplicity of the sequence makes screen-printing ideal for poorer quality substrates such as mc-Si as well as Cz. The general trend is to move to larger size substrates – now up to 15cm x 15cm for mc-Si and reduce the wafer thickness (e.g. down to 200  $\mu$ m)

47

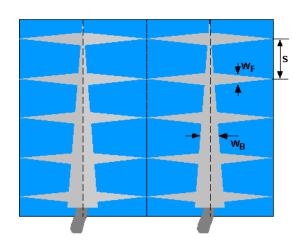

Grid design – traditional (left) or special for a rear-contact structured device

#### **Overview**

Only one high-T step (P-diff. at 900°C)

Sintering of contacts needs only 400°C

- → relatively cheap

- $\rightarrow$  Surfaces has sub-optimal electrical and optical properties

Front:

low lifetime in highly-doped emitter region poorly textured front surface has high reflectivity

#### Back:

high recombination at metal rear resistive losses optical losses via parasitic absorption at metall/Si interface and poor reflectance from rear side

Size:

| 4 inch | 100 x 100 mm <sup>2</sup> | $I_{\rm sc} \sim 3.0  \rm A$   |

|--------|---------------------------|--------------------------------|

| 5 inch | 125 x 125 mm²             | $I_{\rm sc} \sim 4.9  {\rm A}$ |

| 6 inch | 156 x 156 mm <sup>2</sup> | $I_{sc} \sim 8.5  \text{A}$    |

# "Solar Energy" WS 2014/2015

Lecture 7: Part 1: Fabrication of Silicon Solar Cells Part 2: Thin Film Crystalline Silicon Solar Cells

#### Prof. Dr. Bryce S. Richards

Institute of Microstructure Technology (IMT), Hermann-von-Helmholtz-Platz 1, 76344 Eggenstein-Leopoldshafen Light Technology Institute (LTI), Engesserstrasse 13, Building 30.34, 76131 Karlsruhe

KIT Focus Optics & Photonics

KIT – Universität des Landes Baden-Württemberg und nationales Forschungszentrum in der Helmholtz-Gemeinschaft

www.kit.edu

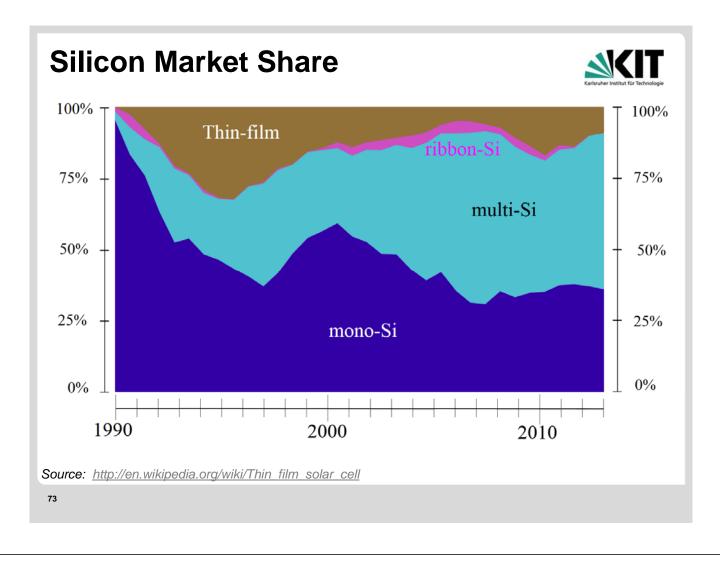

### Thin Film Solar Cells

Why thin film?

- Very energy-intensive process growing MG-Si, and then either Cz c-Si or mc-Si ingots

- Significant losses during wafering process

- Solar cells end up inside a sheet of glass anyway, so why not use the glass as a substrate to deposit onto?

- With good light trapping  $\Rightarrow$  don't need 300  $\mu$ m of Si, 2  $\mu$ m of semiconductor enough (even with Si)

- More uniform product appearance

- Higher throughput

- Demand for silicon exceeding supply

- So there should be a distinct cost advantage....

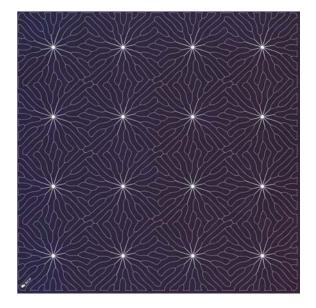

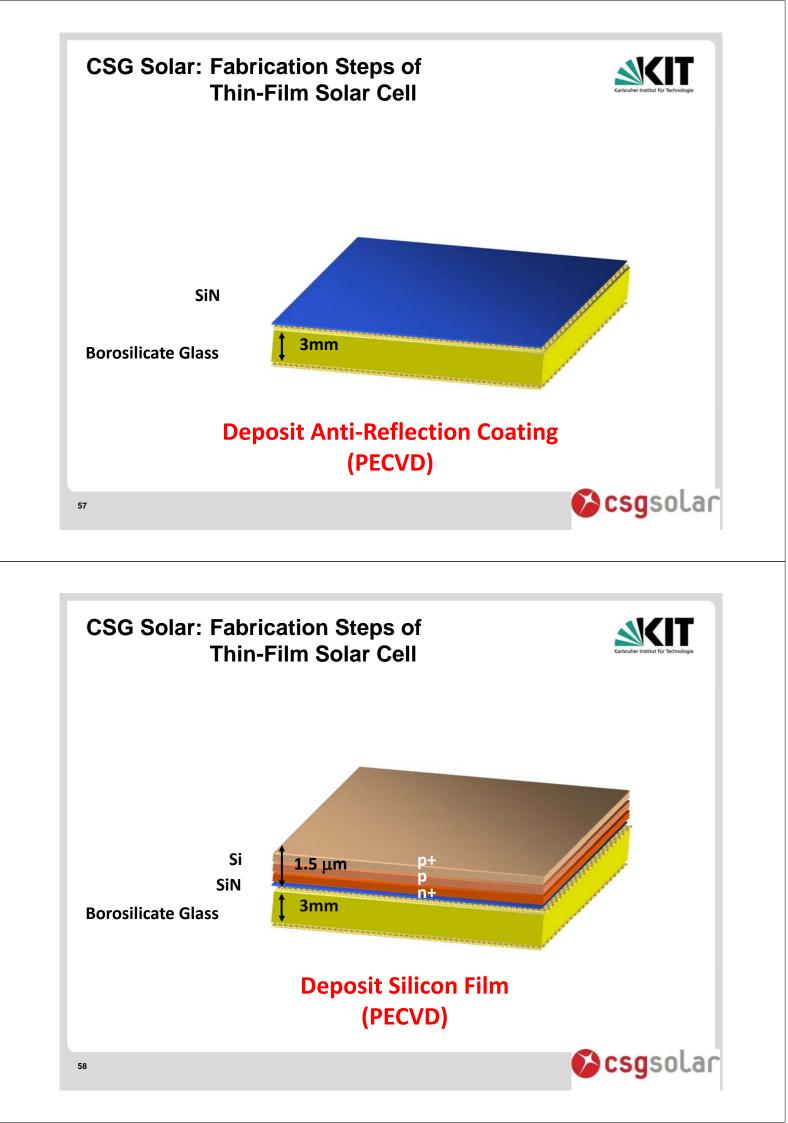

#### Thin Film Solar Cells

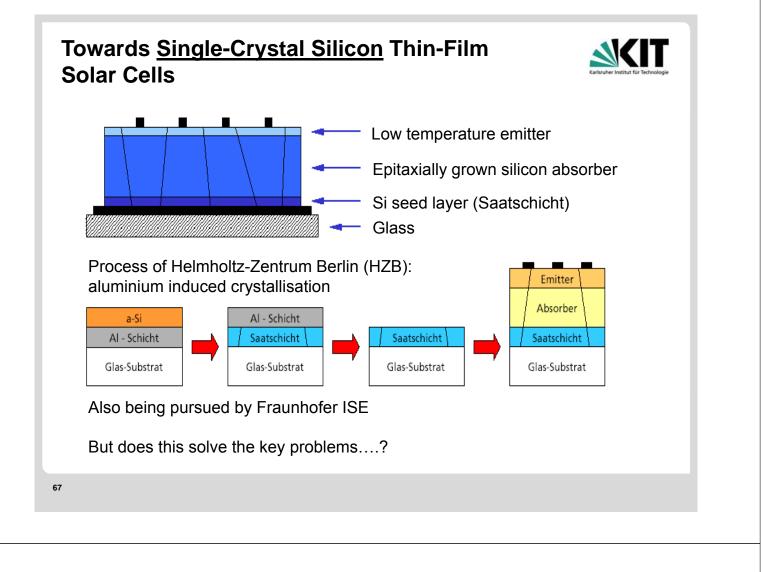

Why crystalline silicon thin film?

• No degradation like with amorphous silicon (a-Si) solar cells

... but still an indirect bandgap so excellent light trapping needed!

Note that this is NOT single crystal silicon

actually small grain polycrystalline Si

also called microcystalline silicon (µc-Si)

Source: <u>http://www.pressebox.de/pressemitteilung/csg-solar-ag/Dr-Ottmar-Koeder-wird-neues-</u> <u>Vorstandsmitglied-fuer-den-Bereich-Produktion-der-CSG-Solar-AG/boxid/186646</u>

53

| ome     | Categories     | FAQs         | About Us                                 | Contact Us                    |         |                    | 7                  | Shopping Cart |

|---------|----------------|--------------|------------------------------------------|-------------------------------|---------|--------------------|--------------------|---------------|

| Get yoı | ır domain ı    | name to      | day, we ma                               | ike it easy                   | Search: | Enter Keyword or F | <sup>o</sup> hrase | Search        |

|         |                |              |                                          |                               |         |                    |                    |               |

| Csg     | Solar.c        | om is        | for sale                                 | (Csg Solar)                   |         | )                  | A                  |               |

| Click h | ere to buy Csg | Solar.com fo | or <b>\$1,895</b>                        |                               |         |                    |                    |               |

|         |                |              | ss, or build a site<br>d uniquely your o | e for your personal us<br>wn. | se.     | F                  | 0H<br>41 F         |               |

|         | Buy Nov        | Onl<br>Call  | ly \$1,895<br>us for more inform         | ation: 1-303-893-0552         |         |                    |                    |               |

|         |                |              |                                          |                               |         |                    |                    |               |

|         |                |              |                                          |                               |         |                    |                    |               |

|         |                |              |                                          |                               |         |                    |                    |               |

#### Suntech beendet Entwicklungsarbeiten bei Tochterunternehmen CSG Solar | 29.07.2011

#### > Zurück zur Ausgangsseite

Die CSG Solar AG, Bitterfeld-Wolfen, stellt ihre Tätigkeit endgültig ein. Das teilt die Suntech Power Holdings Co., Ltd., Wuxi mit. Der chinesische Photovoltaikkonzern, der zu den führenden Herstellern von Solarmodulen auf der Basis kristalliner Solarzellen gehört, hatte das deutsche Unternehmen übernommen, nachdem es 2009 in Liquiditätsnot geraten war.

"Die Schließung von CSG wird es uns erlauben, uns besser darauf zu konzentrieren, was wir am besten können: Unsere Kunden weltweit mit leistungsstarken und zuverlässigen kristallinen Solarmodulen zu beliefern", sagt Dr. Zhengrong Shi, Chairman und CEO von Suntech.

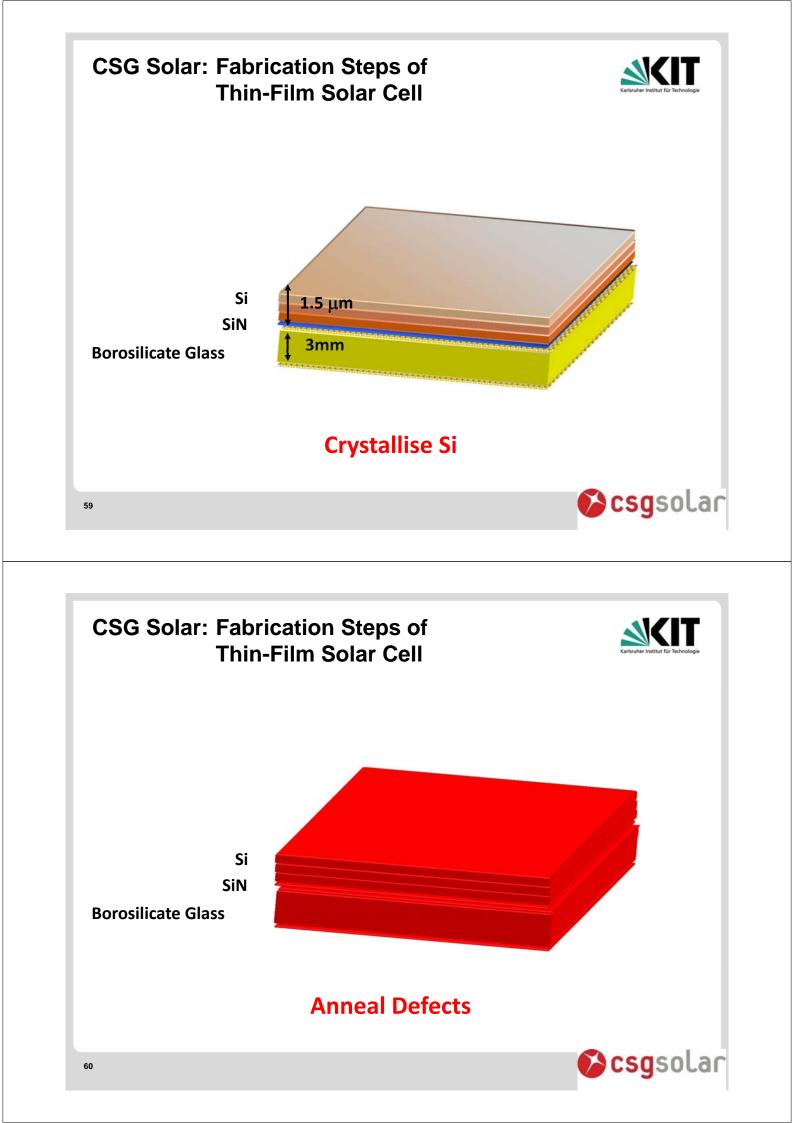

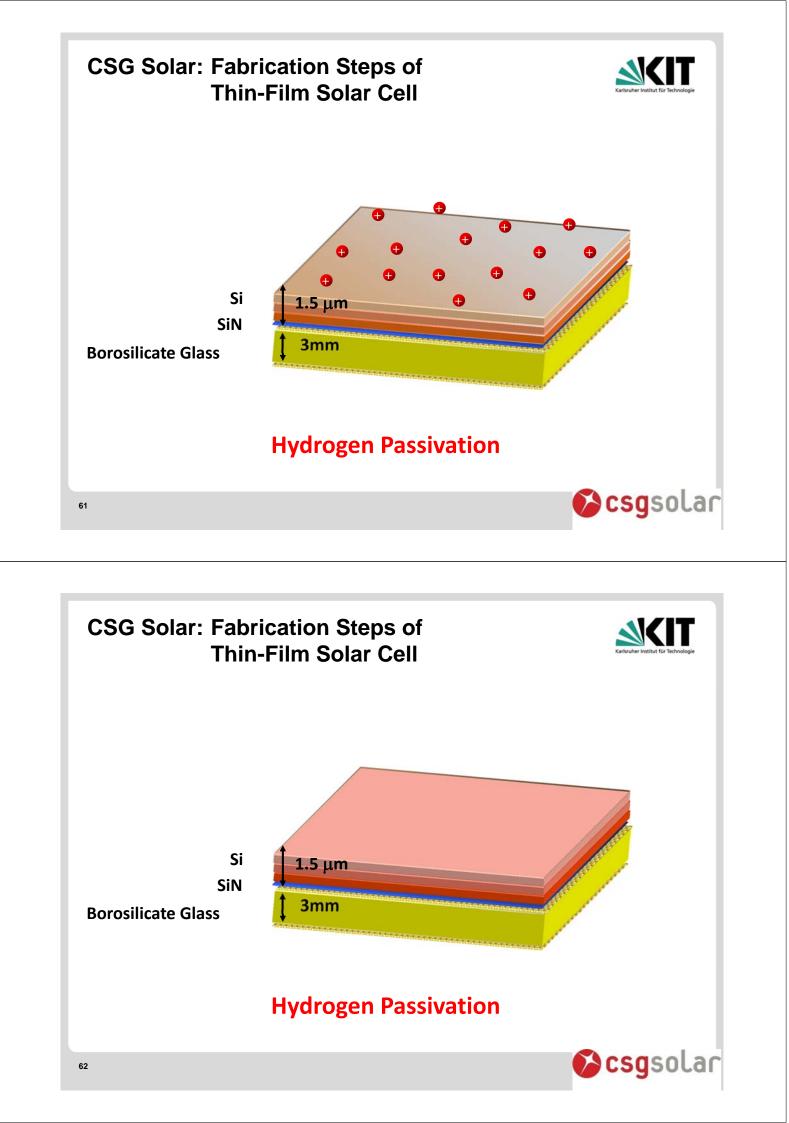

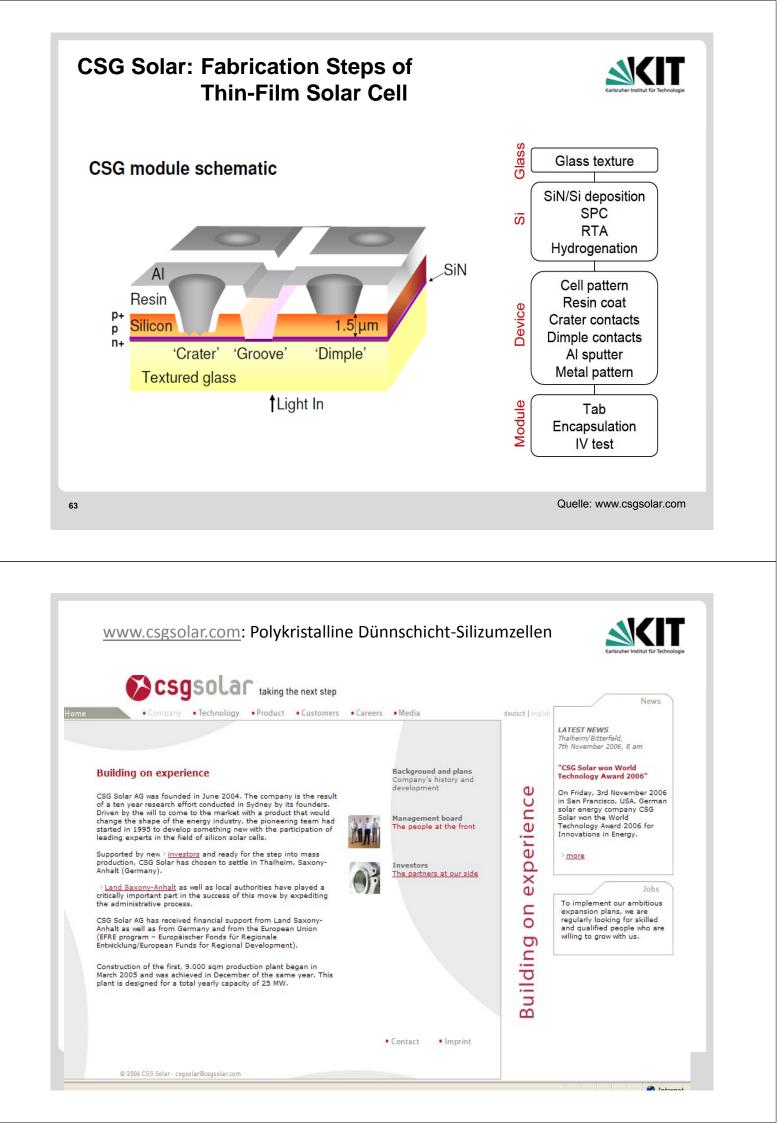

Die CSG Solar AG wurde 2004 durch ehemalige Mitarbeiter der Pacific Solar Inc., Sydney/Australien, gegründet. Das Unternehmen setzte auf eine Technologie, bei der auf Glas zunächst Siliziumnitrid als Antireflexionsschicht und dann nachfolgend Silizium in drei dünnen, unterschiedlich dotierten Schichten abgeschieden wird. Anschließend wurde das Silizium durch Erhitzen kristallisiert. Das brachte Kostenprobleme – nicht zuletzt deshalb, weil für dieses Verfahren hitzebeständiges Borosilikatglas benötigt wird, das deutlich teurer ist als das übliche Solarglas.

Auch die Strukturierung des Moduls sowie Rückseitenbeschichtung, die Durchkontaktierung und das Aufbringen der Leiterbahnen erfolgten mit einem relativ hohen technischen Aufwand. Dennoch erreichte CSG Solar seinerzeit lediglich einen Modulwirkungsgrad von 6,5 Prozent. Das Unternehmen hoffte aber, den Prozess, der von einer Forschergruppe um Prof. Martin Green an der University of New South Wales in Sydney entwickelt worden war, weiter optimieren und den Wirkungsgrad der Module binnen Jahresfrist auf über zehn Prozent steigern zu können. Die Tatsache, dass nunmehr auch Suntech nicht mehr bereit ist, Geld in diese Technologie zu investieren, deutet darauf hin, dass es nicht gelungen ist, das Verfahren wirtschaftlich zu gestalten. Suntech Power Holdings

# CSG Solar

Why did it fail?

- Never got over 10% for full size (~1m<sup>2</sup>) modules

- Cannot ignore the balance-of-systems (BoS) costs

⇒ remember from Dr. Goldschmidt's lecture that

these are area-related

- Global recession started in 2009.... (reduced demand)

... combined with huge amount of poly-Si manufacturing plants coming online (over supply)...

... meant that the bottom dropped out of the wafer-based silicon solar market

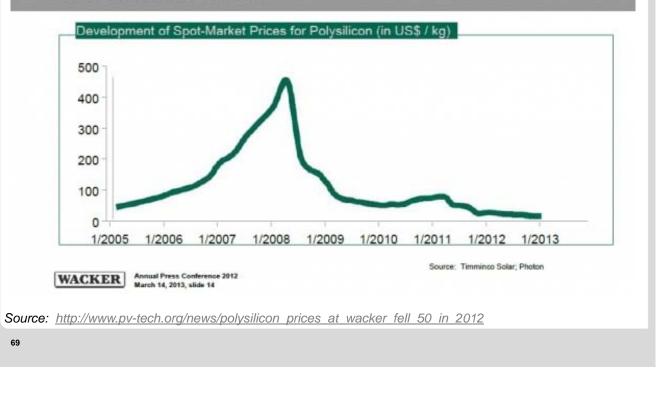

#### **Silicon Prices**

#### AVERAGE PRICE OF SOLAR-GRADE SILICON FELL BY HALF IN PAST YEAR

#### **Silicon Prices**

#### **PV Spot Price**

(Annoucement) We've added new columns for mono-si module and

high-efficiency/mono-si cell and adjusted standard for wafers. Any questions, please don't hesitate to <u>contact</u> <u>us</u> ] !

Price quotes updated weekly (\$US)< Limitations on Liability > Methodology

| Polysilicon                                            |       |       | 2014/11/12 update |                   |       |  |  |

|--------------------------------------------------------|-------|-------|-------------------|-------------------|-------|--|--|

| Item                                                   | High  | Low   | Avg               | Chg               | Chart |  |  |

| Polysilicon Price (Per KG)                             | 23.50 | 19.00 | 20.700            | - (0 %)           | ~~~   |  |  |

| Wafer                                                  |       |       |                   | 2014/11/12 update |       |  |  |

| Item                                                   | High  | Low   | Avg               | Chg               | Chart |  |  |

| Super High Efficiency Multi-Si Wafer (156mm x 156mm) 🗰 | 1.02  | 0.93  | 0.965             | <b>•</b> (3.76 %) | ~~~   |  |  |

| High Efficiency Multi-Si Wafer (156mm X 156mm) 🛛 🗰     | 0.93  | 0.87  | 0.900             | <b>- (</b> 0 %)   | ~~~   |  |  |

| Mono-Si Wafer (156mm x 156mm)                          | 1.20  | 1.10  | 1.155             |                   | ~~~   |  |  |

\*The efficiency of cell made from super high-efficiency wafer is higher than mainstream product, thus its price is higher than mainstream wafer price.

Source: http://pv.energytrend.com/pricequotes.html

71

#### **Silicon Prices**

| Cell 2014/11/12 upd                          |  |                                          |      |       |                    |       |  |

|----------------------------------------------|--|------------------------------------------|------|-------|--------------------|-------|--|

| Item                                         |  | High                                     | Low  | Avg   | Chg                | Chart |  |

| High Efficiency Multi-Si Cell (Per Watt) 🛛 🕬 |  | 0.43                                     | 0.33 | 0.340 | <b>-</b> (0 %)     | ~~~   |  |

| Taiwanese Multi-Si Cell (Per Watt)           |  | 0.34                                     | 0.32 | 0.325 | <b>◆</b> (-1.52 %) | ~~~   |  |

| Chinese Multi-Si Cell (Per Watt)             |  | 0.34                                     | 0.30 | 0.320 | <b>•</b> (0.31 %)  | ~~~   |  |

| Mono-Si Cell (Per Watt) 🛛 🗰                  |  | 0.47                                     | 0.40 | 0.425 | <b>-</b> (0 %)     | ~~~   |  |

| Mono-Si Cell with PERC (Per Watt)            |  | become our MI member to access full data |      |       |                    |       |  |

\*The definition of high-efficiency multi-si cell is cell with efficiency above 17.8%.

| Module 20                       |      |      |       |                 |       |  |

|---------------------------------|------|------|-------|-----------------|-------|--|

| Item                            | High | Low  | Avg   | Chg             | Chart |  |

| Multi-Si Module (Per Watt)      | 0.69 | 0.53 | 0.578 | <b>-</b> (0 %)  | ~~~   |  |

| Mono-Si Module (Per Watt) 🛛 🛛 🗛 | 0.74 | 0.61 | 0.630 | <b>- (</b> 0 %) | ~~~   |  |

Source: http://pv.energytrend.com/pricequotes.html

# Summary

- Carlsruher Institut für Technologie

- Simple and robust fabrication process for screen-printed PV

- High energy intensity of crystalline silicon in general

- mc-Si and c-Si solar cells remain dominant mostly lowertech screen-printed devices

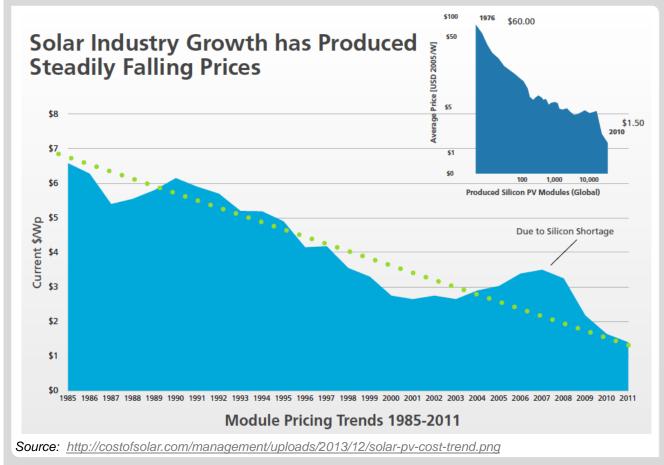

- Success of a technology has more to do with timing, the economic climate and what government policy in key countries around the world is doing than the technical merit ⇒ frustrating for an engineer!

- Hence, wafer based Si presents all other technologies with a "moving goal post" ⇒ always incrementally decreasing costs and increasing η ⇒ technology expected to dominate

- for at least another decade